by Anoop Aaha | The sensors in autonomous vehicles continuously generate a high volume of data in real time about the environment surrounding the car. The vehicles need new hardware architectures to be able to process this data quickly and make decisions that enable self driving. Catapult®, the industry’s leading High-Level Synthesis (HLS) platform, provides a new paradigm of designing silicon at a higher level of abstraction – in C++/SystemC – that improves the hardware design by an order of magnitude. It also enables a seamless verification of C++ and RTL as well as combines with PowerPro® for measurement, exploration, analysis, and optimization of RTL power. The algorithmic-intensive designs for autonomous vehicles are a perfect fit for HLS – and the methodology has been successfully adopted by major semiconductor suppliers in the automotive space.

Autonomous vehicles require a sophisticated framework of sensors to function. These sensors include LiDAR, Radar, video, etc. that continuously generate a high volume of data in real time about the environment surrounding the car. The sensors constantly send their output for analysis to powerful domain controllers connected to a processing unit. The discrete data from different sensors are then merged to create meaningful information related to the vehicle’s location, speed, direction and surroundings. This process is known as sensor fusion.

Sensor Fusion is typically done using custom hardware – either FPGA or ASICs. The data is then processed to make decisions that impact the ADAS systems –such as turns, breaks or speed adaptation. The hardware incorporates algorithms which involve machine learning in sophisticated artificial intelligence (AI) applications to facilitate real-time processing of the sensor data.

Overview

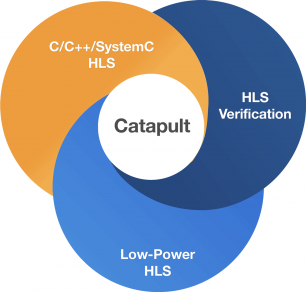

The Catapult High-Level Synthesis (HLS) Platform empowers designers to use industry-standard ANSI C++ and SystemC to describe functional intent and move up to a more productive abstraction level.

The Catapult High-Level Synthesis Platform empowers designers to use industry-standard ANSI C++ and SystemC to describe functional intent and move up to a more productive abstraction level.

From these high-level descriptions, Catapult generates production-quality RTL. By speeding time to RTL and by automating the generation of bug free RTL, Catapult significantly reduces the time to verified RTL. The Catapult Platform pairs synthesis with the power of formal C property checking to find bugs early at the C/C++/SystemC level and to comprehensively verify source code before synthesis.

Catapult’s advanced power optimizations automatically provide significant reductions in dynamic power consumption. The highly-interactive Catapult workflow provides full visibility and control of the synthesis process, enabling designers to rapidly converge upon the best implementation for power, performance, and area.

Key Features/Benefits

- Native SystemC and ANSI C++ synthesis

- Write 80% less code to save time and make debug easy

- Simulate 100-1000x faster for reduced verification time

- RTL optimized for power, performance, area, and RTL verification

- Tightly integrated formal C property checking for C based verification

C/C++/SystemC HLS

Catapult is the only High-Level Synthesis Platform to natively support both ANSI C++ and SystemC, giving designers the freedom to work in their preferred language and move up to a more productive abstraction level. Abstract models synthesizable by Catapult typically require 80 percent less hand-written code and can simulate up to 1,000 times faster than synthesizable RTL.

From these high-level descriptions, Catapult generates optimized Verilog or VHDL, ready for production RTL synthesis and verification flows. The platform gives designers control over which regions are optimized and the ability to work top-down or bottom-up, which is required for RTL IP integration.

The database and smart caching techniques provide at least a 10X capacity improvement, making the synthesis of large subsystems possible. The synthesized RTL is optimized for power, performance, area, and timing closure. This verification-optimized RTL code is ready to be deployed into corporate verification methodologies, including UVM-based flows.

Key Features

- Native dual-language support of SystemC and C++

- Control and predictability required to achieve design closure on complex designs

- Comprehensive design management and assembly systems with 10X capacity

- Integration with standard functional verification methodologies

- Verification-optimized RTL code

HLS Verification

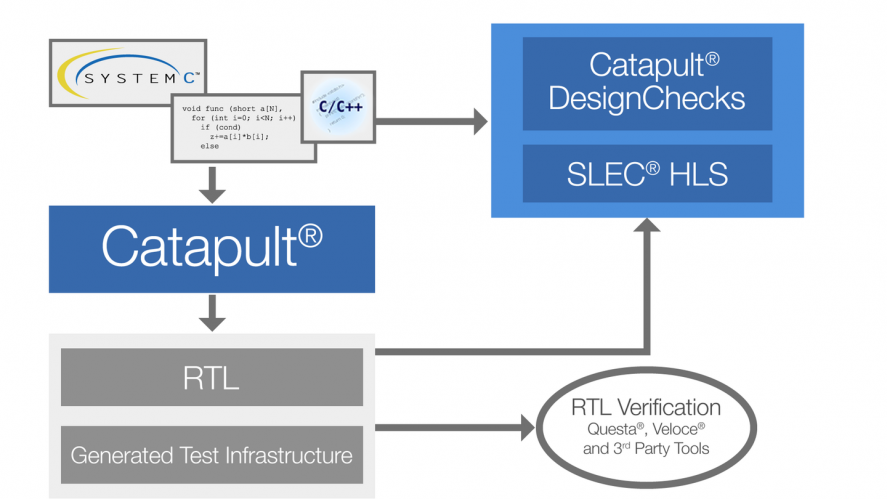

High-Level Synthesis (HLS) Verification with the Catapult Platform has three categories:

- Automatic/formal checking of users’ HLS targeted C++/SystemC code finding errors before synthesis.

- Simulation based verification comparing functionality of users C++/SystemC source with generated RTL including metrics such as coverage and assertions.

- Formal verification of equivalence of the users’ C++/SystemC code with the generated RTL from synthesis Catapult® DesignChecks formally verifies the design to find bugs and issues in the user’s code before starting the HLS process. It identifies defective code using static checks for defined properties and comprehensively verifies assumptions through formal proofs of user-defined assertions.

The SCVerify flow in Catapult automatically generates the verification infrastructure for verifying the functionality of the HLS generated RTL against the users original source code and re-uses the original C++/SystemC testbench. In addition to functional comparison, it includes translation of assertions and coverage from the HLS level to the RTL level for coverage closure. SCVerify supports Mentor QuestaSim/ModelSim, Synopsys VCS and Cadence IUS/NCSim simulation environments.

The UVMf flow in Catapult automatically generates a complete UVM environment using the UVM Framework (UVMf). The automatic generation includes re-use of the original C tests wrapped in SystemVerilog as a sequence generator, the source HLS C model as a UVM predictor, a scoreboard that will automatically compare the results from the HLS C model to the resulting RTL in simulation. The environment also automatically generates a small test set of SystemVerilog constrained-random UVM sequences into each of the user agents that the user could use as a starting point to easily add more tests. The UVMf flow supports Mentor QuestaSim.

SLEC HLS formally proves the equivalence of the Catapult HLS generated RTL to the designer’s original C/C++/SystemC code. It is based on patented sequential analysis technology which enables it to finds design errors that other tools miss because it can compare the functionality of a HLS system-level model with its corresponding synthesized RTL design across all possible input sequences.

Key Features

- Assertion and property-based verification for HLS models

- Find difficult to detect bugs without writing complex testbenches

- Sequential equivalence comparison of HLS and RTL for Independent verification

- Replaces time consuming simulation regressions with fast results

- Automatic generation of RTL verification environment re-using users C/C++/SystemC testbench

- Compares functionality of users C/C++/SystemC behavior interactively with RTL

Low-Power HLS

Catapult Low-Power (LP) is the industry’s first High-Level Synthesis (HLS) tool that targets power as an optimization goal. It takes advantage of PowerPro®’s best-in-class power analysis and optimization technology by embedding it at the core of the HLS engine.

This provides a closed-loop optimization flow across power, performance and area from architecture definition to RTL implementation.

A designer uses Catapult LP to explore different hardware architecture and measures the power, performance and area of each solution. Catapult’s interactive analysis tools assist in design refinement. During the synthesis process, Catapult LP automatically performs fine grained power-saving optimizations aimed at minimizing switching activity in the RTL to deliver the greatest power savings.

Key Features

- C/C++/SystemC HLS with built-in power awareness

- Measures and compares power across multiple architectures

- Automatically synthesizes low-power RTL with fine grained optimizations

- Leverages PowerPro’s deep sequential analysis technology

- Sequential clock gating for fine grained power reduction of register, clock tree, and logic power

- Loop and memory optimization for architecture exploration and optimization.

Conclusion

Autonomous designers are grappling with new silicon architectures optimized for neural computing and computer vision to make autonomous vehicle solutions better and faster to market than ever before.

To have the most efficient implementation of the silicon for ADAS, they need to move up the abstraction layer for higher design and verification productivity.

Existing RTL-based design methodologies cannot scale to meet this demand, since SoC designs for autonomous vehicles are too complex to design efficiently by hand-coding RTL. Additionally, verification times are escalating out of control, making it necessary to verify designs as early as possible. HLS is proven to deliver higher quality algorithmic-based designs faster and more efficiently than RTL for autonomous drive systems.

Anoop Aaha, Market Development Manager, digital design and implementation solutions for Mentor, A Siemens Business. Reproduced with special permission. ©2019 Mentor Graphics Corporation, all rights reserved. This document contains information that is proprietary to Mentor Graphics Corporation and may be duplicated in whole or in part by the original recipient for internal business purposes only, provided that this entire notice appears in all copies. In accepting this document, the recipient agrees to make every reasonable effort to prevent unauthorized use of this information. All trademarks mentioned in this document are the trademarks of their respective owners.